assign #DELAY_TIME ddr_dqs_sdram = (enable_o==1'b0) ? ddr_dqs_fpga : {DQS_BITS{1'bz}};

そこで、このページを参考にさせていただいて、伝播遅延にするためにalways文、ノンブロッキング文で書いてみた。

`timescale 1ps / 1ps

parameter DELAY_TIME = 1500;

wire [DQS_BITS-1:0] ddr_dqs_fpga, ddr_dqs_sdram;

wire [DQ_BITS-1:0] ddr_dq_fpga, ddr_dq_sdram;

reg [DQS_BITS-1:0] ddr_dqs_fpgan, ddr_dqs_sdramn;

reg [DQ_BITS-1:0] ddr_dq_fpgan, ddr_dq_sdramn;

always @ *

if (enable_o == 1'b1)

ddr_dqs_fpgan <= #DELAY_TIME ddr_dqs_sdram;

else

ddr_dqs_fpgan <= #DELAY_TIME {DQS_BITS{1'bz}};

always @ *

if (enable_o == 1'b1)

ddr_dq_fpgan <= #DELAY_TIME ddr_dq_sdram;

else

ddr_dq_fpgan <= #DELAY_TIME {DQ_BITS{1'bz}};

always @ *

if (enable_o == 1'b0)

ddr_dqs_sdramn <= #DELAY_TIME ddr_dqs_fpga;

else

ddr_dqs_sdramn <= #DELAY_TIME {DQS_BITS{1'bz}};

always @ *

if (enable_o == 1'b0)

ddr_dq_sdramn <= #DELAY_TIME ddr_dq_fpga;

else

ddr_dq_sdramn <= #DELAY_TIME {DQ_BITS{1'bz}};

assign ddr_dqs_fpga = ddr_dqs_fpgan;

assign ddr_dq_fpga = ddr_dq_fpgan;

assign ddr_dqs_sdram = ddr_dqs_sdramn;

assign ddr_dq_sdram = ddr_dq_sdramn;

parameterの値はDQS_BITSは2で、DQ_BITSは16だ。

inoutの信号はregで宣言するとエラーになるのでregで宣言する信号は中間ノードとして、wireで宣言したinoutの信号にassignで代入している。

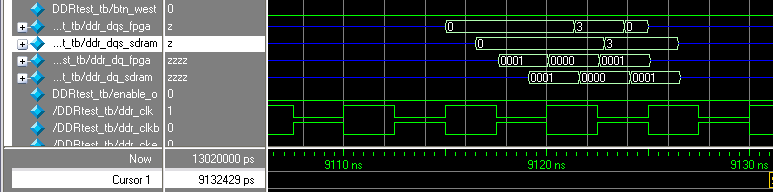

ModelSimの波形を下に示す。

上の図でddr_dqs_fpgaを1500ps遅延させてddr_dqs_sdramに入れていても、0-3-0と正常に遷移している。

もう少しバグを取ったらDDR SDRAMが正常に動作してREAD時のデータ出力までするようになった。でもdata_validが1の時に出力データが出ない。もう少しデバックが必要のようだ。

ともかくDDRが動作するようになってよかった。いろいろなWebサイトに助けられている。このブログも他の方の役に立てていれば良いと思った。