VGAの表示領域は800×600で72Hz。とりあえずはテストのためにビットごとに色を+1で作る回路をつけて状況を見ようと思っている。でも、仕事が忙しくなれば家でも仕事をするかもしれないので、中断するかもしれない。

まずはfpga-lab.orgさんの3月25日の徒然日記で知ったVGA Video OutputでVGAフォーマットのお勉強。その結果、仕様を一部だが決定した。

DDR SDRAMコントローラを使うために、Spartan3E Starter KitでVGAコントローラを作ることにした。解像度は800×600、垂直同期の周波数は72Hzとする。そうするとピクセルクロックは50MHzとなる。このピクセルクロックはSpartan3E Starter Kitに搭載される50MHzの水晶発信器をDCMで等倍して作ることにする。

水平同期関係のパラメータは、表示領域が800ピクセル、Front Porchは56ピクセル、Back Porchは64ピクセル、水平同期パルスは120ピクセルとなる。

一方、垂直同期関係のパラメータは、表示領域が600ライン、Front Porchが37ライン、Back Porchは23ライン、垂直同期パルスは6ラインとなる。

画素のフォーマットはSpartan3E Starter KitではRGBそれぞれ1ビットずつの3ビットが必要である。それぞれを1バイトのビット1に割り付ける。更に4バイトごとに整列させるためにダミーバイトを1つつける。

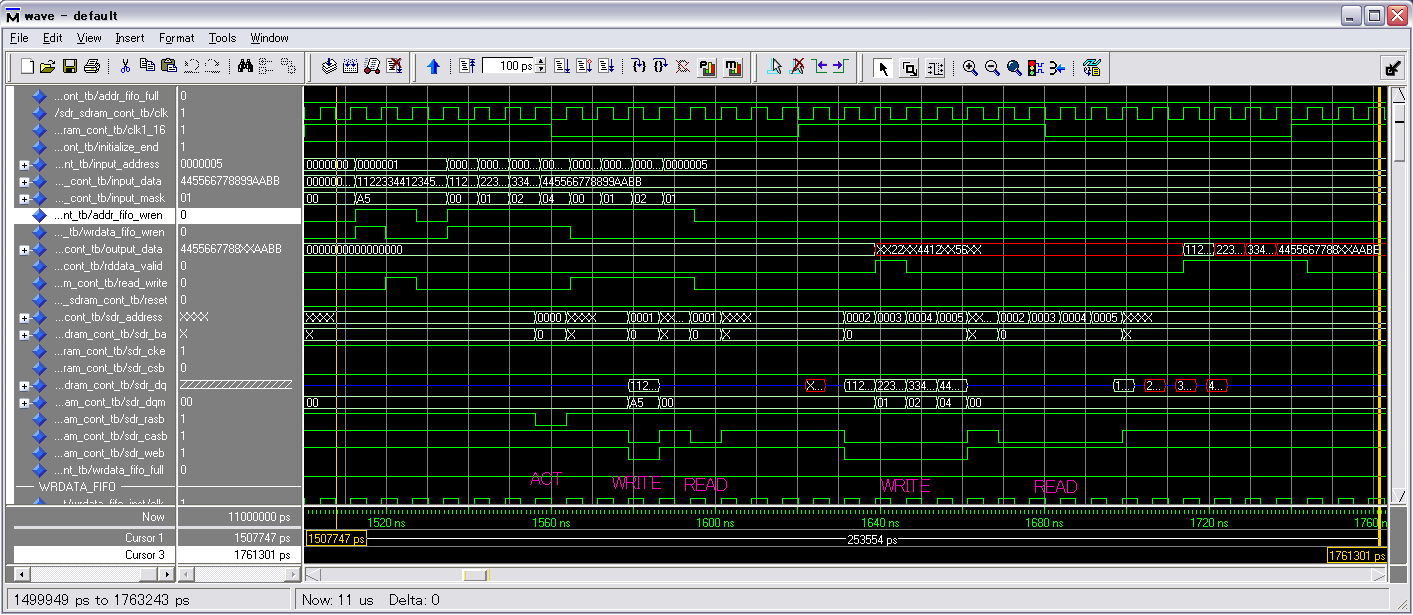

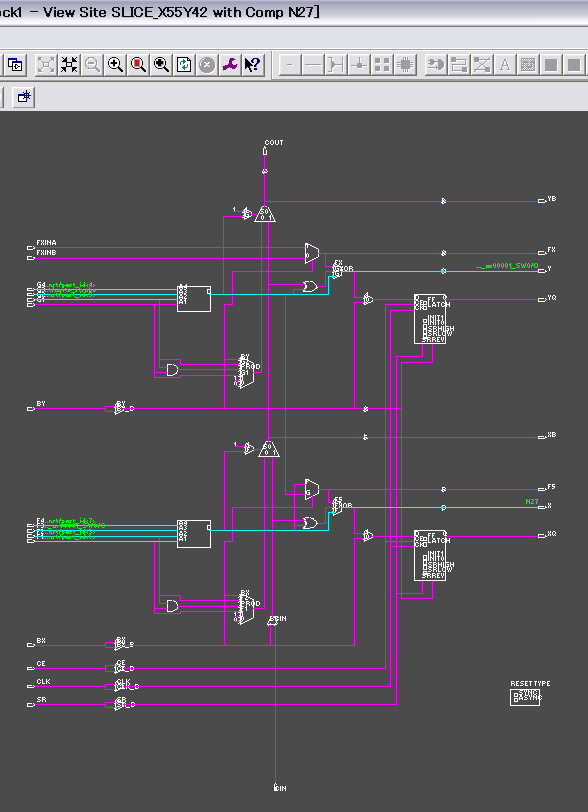

Spartan3E Starter KitのDDR SDRAMは16ビット幅であるので、1クロックで4バイト読み出しが出来る。(16ビット×2) これは4バイトなので、VGAの1ドット分となる。DDR SDRAMは100MHzで動作しているので、画面描画のために、フルにDDR SDRAMから読み出していると50/100でDDR SDRAMの帯域の1/2を占有することになる。あとの1/2でDDR SDRAMにプロセッサからアクセスしたり、DMA(しないけど)したりすることになる。

現在のDDR SDRAMコントローラは、リードしたデータを読み出す場合にデータのみを出力しているが、VGAコントローラとプロセッサなどのほかのマスタ・デバイスのアクセスを分けるために、2ビット分のIDを付加する。

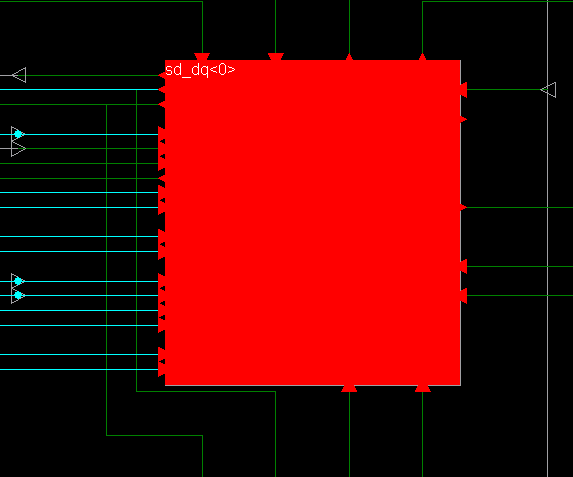

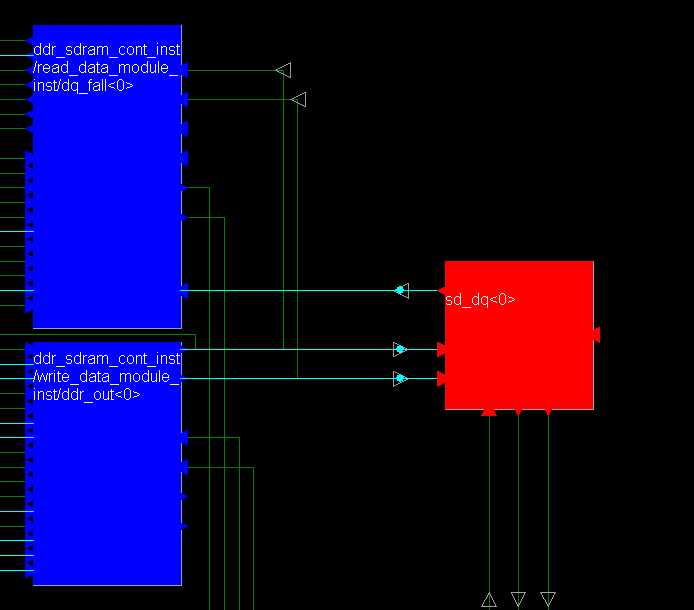

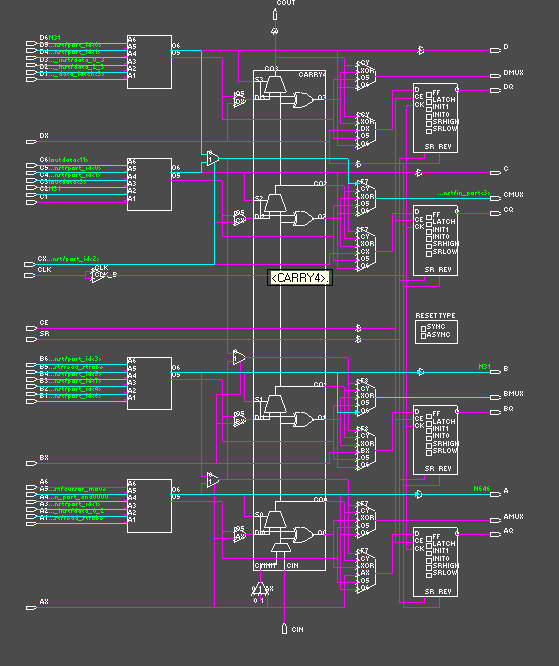

VGAコントローラ、プロセッサなどのほかのマスタ・デバイス、アービタ、DDR SDRAMコントローラのデータパスのブロック図を下に示す。