今回は、3x3のラプラシアン・フィルタの式のみを、以前Vivado HLSのサンプルしてやってみた axi lite を元に変更してみようと思う。多分、計算式がとっても簡単なので、ハードウェア化のメリットは無いどころか、ソフトウェアよりも遅くなるかもしれないがやってみようと思う。

(2013/10/05:注 図などを大幅に書き換えました)

以前やった Vivado HLS のaix liteサンプルの記事を示す。

Vivado HLSのExampleを試してみる1(axi_lite の生成)

Vivado HLSのExampleを試してみる2(シミュレーションと合成)

Vivado HLSのExampleを試してみる3(インターフェイス)

Vivado HLSのExampleを試してみる4(C/RTL Cosimulation)

Vivado HLSのExampleを試してみる5(IPにした)

Vivado HLSで作ったaxi_lite IPをテストした

Vivado HLSのプロジェクトをxc7z020clg484-1で作った。

Cのテストベンチを作製して、Cのシミュレーションを行った。結果は当然といえば当然に成功だった。

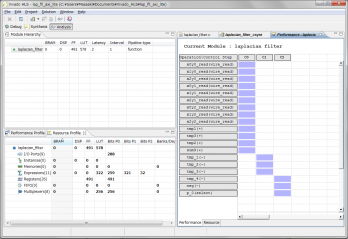

C Synthesis ボタンをクリックして、CからHDLへの合成を行った。成功した。

しかし、FFが 330個、LUTが 582個、使用されている。多い気がする。8を掛けるところは、3ビット左シフトすればよいのでは?更にレイテンシ 2 クロックで、インターバルが 3 クロックなので、これではダメだ。パイプラインにしないとね。

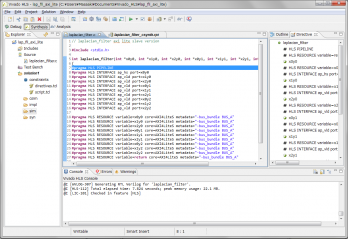

パイプラインにするために、PIPLINE Directive を入れよう。

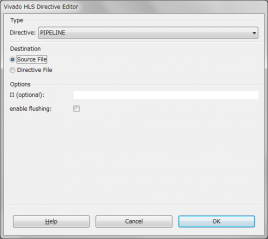

右端のウインドウのDirective タブをクリックして、laplacian_filter の右クリックメニューから Insert Directive を選んだ。

Vivado HLS Directive Editor でPIPLINE Directive を選択して、Destination の Source File のラジオボタンをクリックした。OKボタンをクリックした。

#pragma HLS PIPELINE が追加された。

これで、C Synthesis ボタンをクリックして、CからHDLへの合成を行った。

レイテンシは 2 で変化がないが、インターバルが 1 になって、毎クロック、データを入力できるようになった。

FFは 491個で大幅に増えたが、LUTは 578個で少し減った。