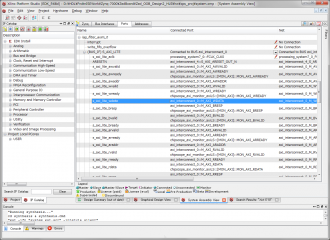

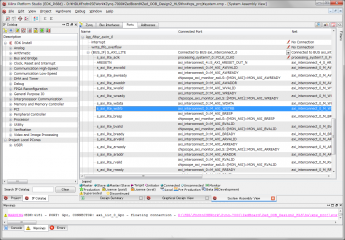

・XPSプロジェクトで、Generate Netlistが終了した。今度は、system_lap_filter_axim_0_wapper のLUT使用率が586になっていて良い感じだ。

・Poject Navigator に戻って、論理合成、インプリメント、ビットストリームの生成を行った。成功した。

・FPGA Editor を立ちあげて、lap_filter_axim_0 を見ると、lap_filter_axim_LiteS_if_Uがあった。これで一安心。

・SDKを立ちあげ、SDカードに入れるブートイメージを作製した。

・BOOT.bin をSDカードに入れて、Linuxをブート。

・lap_filte_axim のデバック・コンフィギュレーションを作って、デバック。(手順はかなり省略しています。詳しい手順は、”Vivado HLSで作ったラプラシアン・フィルタAXI4 Master IPを使う2”をどうぞ)

・まずは、ソフトコアで作ったラプラシアン・フィルタ・ソフトウェアを起動して実行した。(詳しくは、”ソフトウエアのプロファイリング4(ハードウェアと同じ方式)”をどうぞ)

・lap_filte_axim を実行するソフトウェアを実行すると、下の写真のようになった。

・画面の1/4しか、書き込んでいないみたいだ。ショック。。。

・ChipScope Pro を仕掛けておいたので、起動した。下に、WVAILD の立ち上がりでトリガを掛けた時の波形を示す。

・Write Address Channel を拡大してみた。なにかおかしい?

・Read Address Channel を拡大すると理由がわかった。Write Address Channel のアドレス増加ステップがデータバス幅 32/8 = 4 ではなくて、1 だ。

HDLコードの Writeアドレスの増加ステップがおかしかったので、修正を行った。