”Vivado HLS で生成した AXI4 Master DMA IP を使用したカメラ画像表示システム4(ILAコアの挿入2)”の続き。

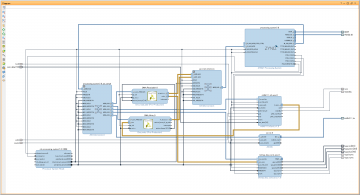

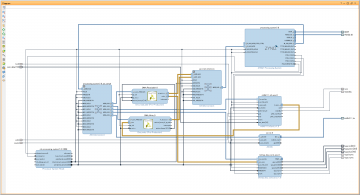

前回、Vivado HLS で生成した AXI4 Master DMA IP を使用したカメラ画像表示システムが動作した。しかし、ブロックデザイン上で挿入したILA コアとネットリストの信号を観察するため入れたILA コアが残ってしまっている。それを削除した。

まずは、ブロックデザイン上で挿入したILA コアを削除しよう。

Debug にマーキングされた配線を複数選択して、右クリックし、右クリックメニューからClear Debug を選択する。

ILA コアの system_ila が削除された。

これで、ブロックデザイン上で挿入したILA コアが削除された。

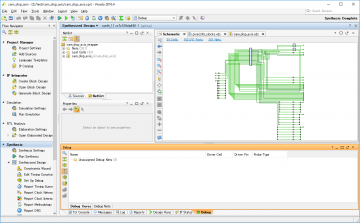

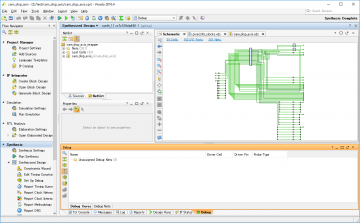

次に、ネットリストの信号を観察するため入れたILA コアを削除する。

論理合成を行って、成功後に表示されるSynthesis Completed ダイアログで Open Synthesized Design を選択した。

Synthesized Design が表示された。Tools -> Set Up Debug... を選択した。

Set Up Debug ダイアログが表示された。Next ボタンをクリックした。

Existing Debug Nets で、Disconnect all net and remove debug cores を選択した。

Set Up Debug Summary が表示された。Finish ボタンクリックした。

ネットリストの信号を観察するため入れたILA コアが削除された。

確か、制約ファイルの ILA コア関連の制約は削除されたが、1つ ILA コアの制約が残っていたので、手動で削除した。

インプリメント、ビットストリームの生成を行った。結果を示す。

ILA コアが入る前と同等のリソース使用量になった。

ハードウェアをエクスポートして、SDK を立ち上げて、カメラ画像をディスプレイに表示してみたところ正常に表示された。

前回、Vivado HLS で生成した AXI4 Master DMA IP を使用したカメラ画像表示システムが動作した。しかし、ブロックデザイン上で挿入したILA コアとネットリストの信号を観察するため入れたILA コアが残ってしまっている。それを削除した。

まずは、ブロックデザイン上で挿入したILA コアを削除しよう。

Debug にマーキングされた配線を複数選択して、右クリックし、右クリックメニューからClear Debug を選択する。

ILA コアの system_ila が削除された。

これで、ブロックデザイン上で挿入したILA コアが削除された。

次に、ネットリストの信号を観察するため入れたILA コアを削除する。

論理合成を行って、成功後に表示されるSynthesis Completed ダイアログで Open Synthesized Design を選択した。

Synthesized Design が表示された。Tools -> Set Up Debug... を選択した。

Set Up Debug ダイアログが表示された。Next ボタンをクリックした。

Existing Debug Nets で、Disconnect all net and remove debug cores を選択した。

Set Up Debug Summary が表示された。Finish ボタンクリックした。

ネットリストの信号を観察するため入れたILA コアが削除された。

確か、制約ファイルの ILA コア関連の制約は削除されたが、1つ ILA コアの制約が残っていたので、手動で削除した。

インプリメント、ビットストリームの生成を行った。結果を示す。

ILA コアが入る前と同等のリソース使用量になった。

ハードウェアをエクスポートして、SDK を立ち上げて、カメラ画像をディスプレイに表示してみたところ正常に表示された。

コメント