”uart_rx と uart_rx_axi4ls を連結してシミュレーションする1”の続き。

3 軸加速度センサーの RS-422 インターフェースのデータを受けるために uart_rx とその後段の uart_rx_axi4ls を Vitis HLS で作ってきたが、それらを連結してシミュレーションしてみようということで、前回は、Vivado 2020.2 の uart_rx_axi4ls_top プロジェクトを作成し、 uart_rx IP と uart_rx_axi4ls IP を IP Catalog に追加した。そてひ、 uart_rx_axi4ls_top_tb.sv のソースコードを貼った。今回は、Viado でブロックデザインを作成し、ラッパー Verilog HDL ファイルを生成して、論理シミュレーションを行う。

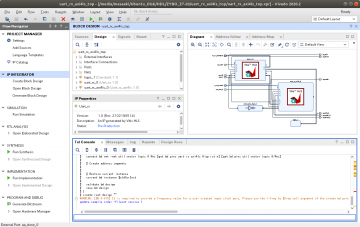

uart_rx_axi4ls_top ブロックデザインを作成し、 uart_rx IP と uart_rx_axi4ls IP を Add IP して追加し、配線を行った。

uart_rx_axi4ls_top ブロックデザインを拡大する。

Address Editor を示す。アドレスマップは実行されていない。

Source ウインドウで uart_rx_axi4ls_top_i を右クリックし右クリックメニューから Create HDL Wrapper... を選択して、Verilog HDL のラッパーファイルを生成した。

Add Sources で”uart_rx と uart_rx_axi4ls を連結してシミュレーションする1”の uart_rx_axi4ls_top_tb.sv ファイルを追加した。

そして、SIMULATION から Run Simulation -> Run Behavioral Simulation を選択して、論理シミュレーションを行った。

シミュレーションの画面が表示された。

Run All ボタンをクリックして、シミュレーションを終了させる。

$STOP 行までシミュレーションを行って、停止している。

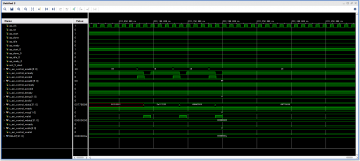

シミュレーション波形を見てみる。

x 軸データ、 y 軸データ、 z 軸データが受かっているか確認するために波形の終わりの部分を拡大した。

キーコード + x 軸データは 0x5a112233 、 y 軸データは 0x00445566 、 z 軸データは 0x00778899 が受かっていることが分かる。これで正解で、成功だ。

3 軸加速度センサーの RS-422 インターフェースのデータを受けるために uart_rx とその後段の uart_rx_axi4ls を Vitis HLS で作ってきたが、それらを連結してシミュレーションしてみようということで、前回は、Vivado 2020.2 の uart_rx_axi4ls_top プロジェクトを作成し、 uart_rx IP と uart_rx_axi4ls IP を IP Catalog に追加した。そてひ、 uart_rx_axi4ls_top_tb.sv のソースコードを貼った。今回は、Viado でブロックデザインを作成し、ラッパー Verilog HDL ファイルを生成して、論理シミュレーションを行う。

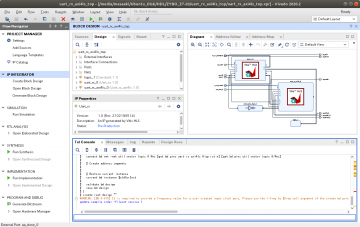

uart_rx_axi4ls_top ブロックデザインを作成し、 uart_rx IP と uart_rx_axi4ls IP を Add IP して追加し、配線を行った。

uart_rx_axi4ls_top ブロックデザインを拡大する。

Address Editor を示す。アドレスマップは実行されていない。

Source ウインドウで uart_rx_axi4ls_top_i を右クリックし右クリックメニューから Create HDL Wrapper... を選択して、Verilog HDL のラッパーファイルを生成した。

Add Sources で”uart_rx と uart_rx_axi4ls を連結してシミュレーションする1”の uart_rx_axi4ls_top_tb.sv ファイルを追加した。

そして、SIMULATION から Run Simulation -> Run Behavioral Simulation を選択して、論理シミュレーションを行った。

シミュレーションの画面が表示された。

Run All ボタンをクリックして、シミュレーションを終了させる。

$STOP 行までシミュレーションを行って、停止している。

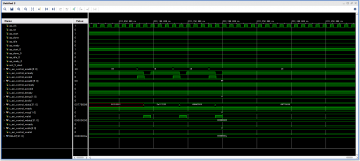

シミュレーション波形を見てみる。

x 軸データ、 y 軸データ、 z 軸データが受かっているか確認するために波形の終わりの部分を拡大した。

キーコード + x 軸データは 0x5a112233 、 y 軸データは 0x00445566 、 z 軸データは 0x00778899 が受かっていることが分かる。これで正解で、成功だ。

コメント