”トリプル・バッファの AXI4-Stream 出力 DMA 1(DMA2axis_3buf)”の続き。

ZYBO Z7-20 用のトリプル・バッファの AXI4-Stream 出力 DMA (DMA2axis_3buf)を Vitis HLS 2022.1 で作成するということで、前回は、ソースコードとテストベンチ・コードを貼って、DMA2axis_3buf プロジェクトを作成した。今回は、C シミュレーション、C コードの合成、C/RTL 協調シミュレーション、Export RTL、Implementation を行った。

C シミュレーションを行った。結果を示す。

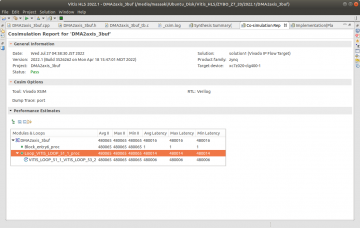

C コードの合成を行った。結果を示す。

レイテンシもリソース使用量も良さそうだ。なお、画像サイズを可変にするとリソース使用量が 1 桁程度増えてしまった。。。

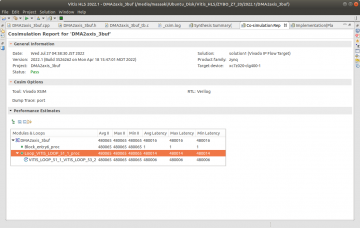

C/RTL 協調シミュレーション結果を示す。

レイテンシは 480016 クロックで良いと思う。

C/RTL 協調シミュレーション波形の一部を示す。

outs_TVALID が 1 にキープされているのが素晴らしい。

Export RTL を行った。

DMA2axis_3buf/solution1/impl ディレクトリに export.zip が生成された。

Implementation を行った。結果を示す。

問題ない結果だと思う。vflip_dma_write の時はどうしたんだろうか?バグがある?

ZYBO Z7-20 用のトリプル・バッファの AXI4-Stream 出力 DMA (DMA2axis_3buf)を Vitis HLS 2022.1 で作成するということで、前回は、ソースコードとテストベンチ・コードを貼って、DMA2axis_3buf プロジェクトを作成した。今回は、C シミュレーション、C コードの合成、C/RTL 協調シミュレーション、Export RTL、Implementation を行った。

C シミュレーションを行った。結果を示す。

C コードの合成を行った。結果を示す。

レイテンシもリソース使用量も良さそうだ。なお、画像サイズを可変にするとリソース使用量が 1 桁程度増えてしまった。。。

C/RTL 協調シミュレーション結果を示す。

レイテンシは 480016 クロックで良いと思う。

C/RTL 協調シミュレーション波形の一部を示す。

outs_TVALID が 1 にキープされているのが素晴らしい。

Export RTL を行った。

DMA2axis_3buf/solution1/impl ディレクトリに export.zip が生成された。

Implementation を行った。結果を示す。

問題ない結果だと思う。vflip_dma_write の時はどうしたんだろうか?バグがある?

コメント