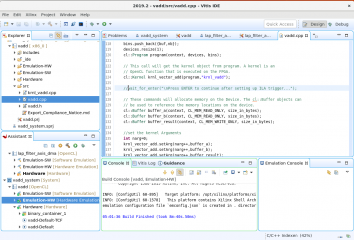

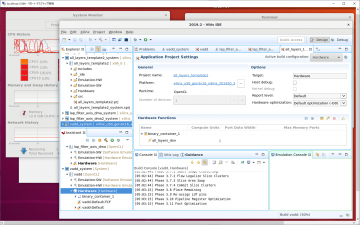

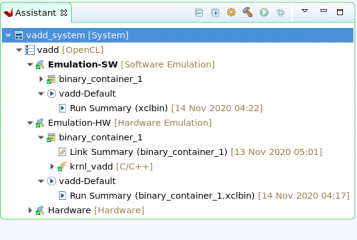

Assistant ウインドウをすべて展開した。

Emulation-SW, Emulation-HW 共に、vadd-Default の下に Run Summary があるのが分かる。

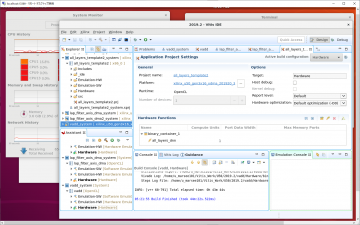

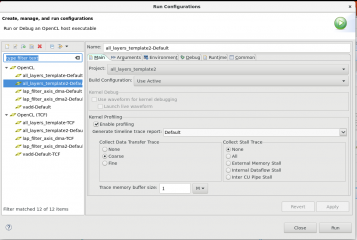

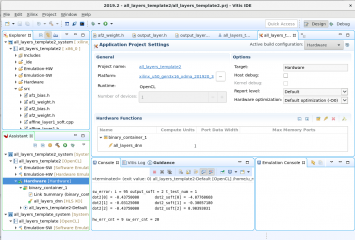

Emulation-SW -> vadd-Default -> Run Summary (xclbin) を右クリックし、右クリックメニューから Open in Vitis Analyzer を選択した。

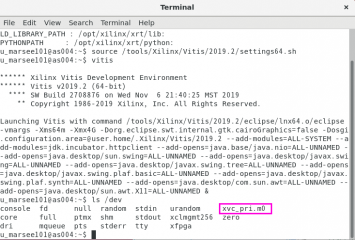

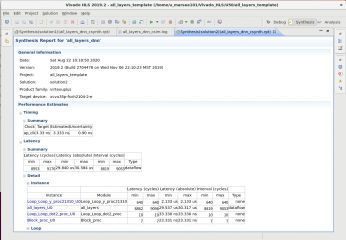

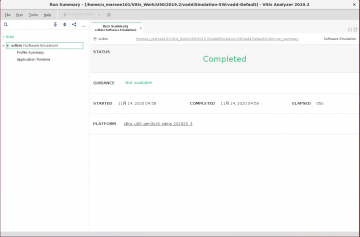

Run Summary ウインドウが表示された。

Profile Summary を示す。

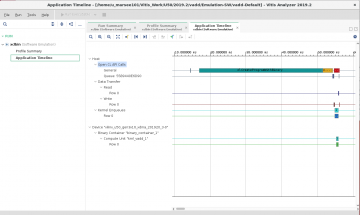

Application Timeline を示す。

波形がある部分を拡大した。

更に拡大した。

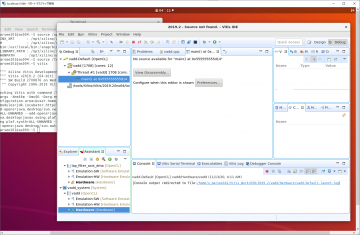

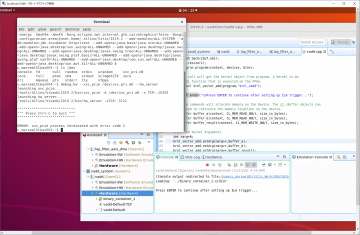

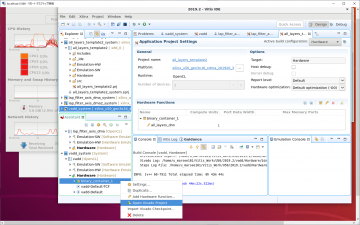

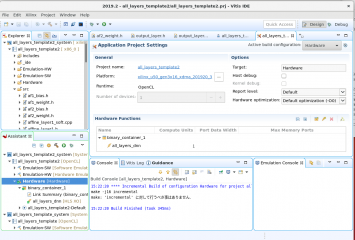

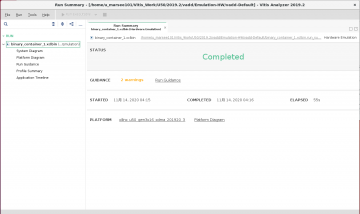

次に、Emulation-HW -> vadd-Default -> Run Summary (binary_container_1.xclbin) を右クリックし、右クリックメニューから Open in Vitis Analyzer を選択した。

Run Summary ウインドウが表示された。

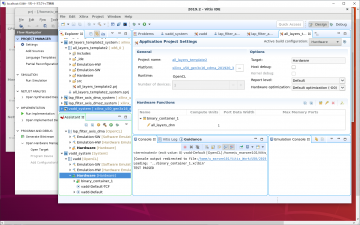

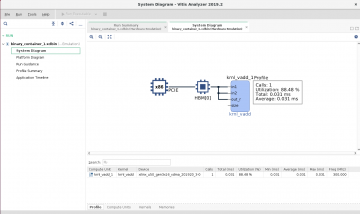

System Diagram を示す。

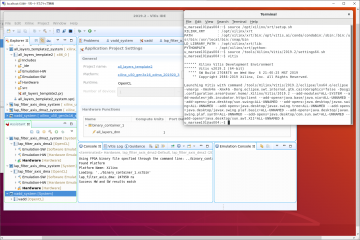

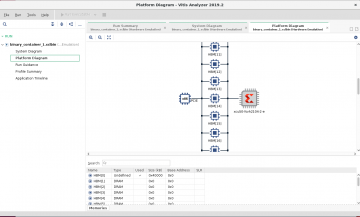

Platform Diagram を示す。

Run Guidance の一部を示す。

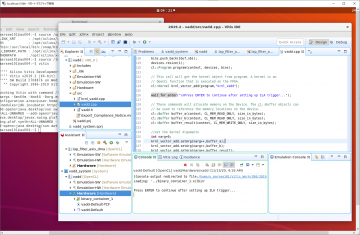

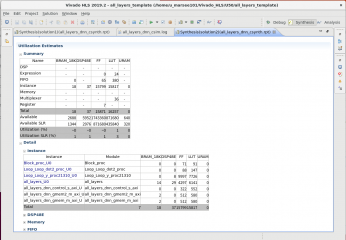

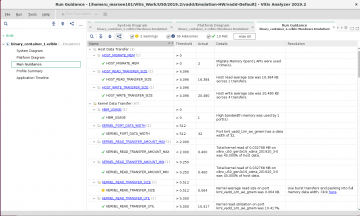

Profile Summary を示す。

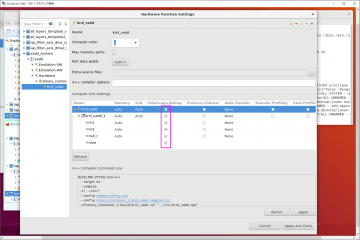

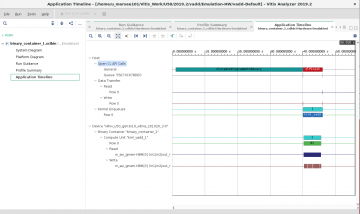

Application Timeline を示す。

拡大した。