まずは、RLOCとU_SET。MIGが生成したUCFファイルの一部を引用する。

INST "infrastructure_top0/cal_top0/tap_dly0/l0" RLOC=X0Y6;

INST "infrastructure_top0/cal_top0/tap_dly0/l0" U_SET = delay_calibration_chain;

RLOC(相対配置制約、原点に対して相対的に位置を指定する。RLOC_ORIGNで原点を指定する)は知っていたのだが、U_SETは知らなかった。U_SETは制約ガイドによると、

デザイン階層全体に分散されているデザインエレメントに RLOC 制約を設定し、1 つの集合にグループ化できるようにします。

ということなので、delay_calibration_chainというグループにグループ化していることになる。

次に、FROM TO制約の場合のDATAPATHONLY。下にMIGが生成したUCFファイルの一部を引用する。

TIMESPEC "TS_CLK" = FROM "clk0" TO "dqs_clk" 18 ns DATAPATHONLY;

ISE13.1のタイミング制約ユーザーガイドの115,116ページの一部を引用する。

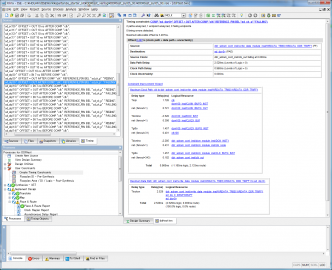

FROM:TO (マルチサ イ ク ル) 制約の解析には、ソースと デステ ィネーション同期エレメント間のクロックスキューが含まれます。クロックスキーは、デスティネーション同期エレメントへのクロックパスからソース同期エレメントへのクロックパスの値を引いて計算されます。クロックスキー解析は、制約の付けられたすべてのクロック に対して自動的に実行されます。 解析には、すべてのデバイスファミリでセットアップ解析、 Virtex-5以降のデバ イ ス の場合はセットアップ とホールド解析の両方が含まれます。FROM:TO制約のクロックスキューを 無視す る 場合は、DATAPATHONLY キーワー ド を使用し ます。

DATAPATHONLY では、解析中にFROM:TO 制約でクロックスキューや位相情報が考慮されないように指定できます。こ のキーワードを使用すると 、データパスのみが解析されます。

DATAPATHONLYを付けると、クロックスキューなどを無視して、データパスのみを解析するそうだ。しかし、Virtex-5以下は新しいバージョンのISEでもホールドの解析はされていないんだったか?確認してみよう。

DIFF_SSTL18_IIという差動のSSTL18の制約があったのか?自分でもこれを指定しておけば良かった。

NET "cntrl0_ddr2_dqs[*]" IOSTANDARD = DIFF_SSTL18_II;

NET "cntrl0_ddr2_dqs_n[*]" IOSTANDARD = DIFF_SSTL18_II;

でも、Spartan-3A Starter Kitのユーザーガイドの117ページでは、DIFF_SSTL18_IIは使っていない。SSTL18_IIを使用している。

BEL、これは知っていたが、書いておく。

INST "top_00/data_path0/data_read_controller0/gen_delay[0].dqs_delay_col0/six" LOC = SLICE_X3Y6;

INST "top_00/data_path0/data_read_controller0/gen_delay[0].dqs_delay_col0/six" BEL = G;

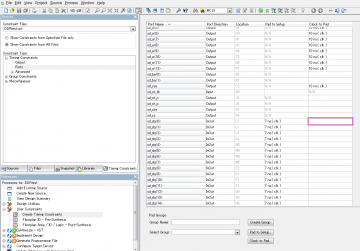

Spartan-3Aでは、スライスに2つのFFが入っている。これをFとGと呼んでいる。これは、FPGA Editorでスライスをダブルクリックして、F=ボタンをクリックしてみるとよくわかると思う。下にその図を示す。

つまり上の制約は、"top_00/data_path0/data_read_controller0/gen_delay[0].dqs_delay_col0/six"というインスタンスがSLICE_X3Y6のスライスの下側のGのFFに割り当てられることを示している。