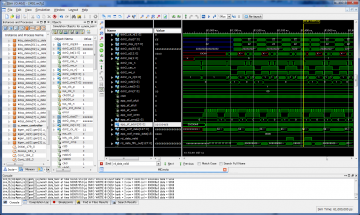

カメラはアプティナ社のMT9T031をカメラモジュールとして使用したカメラを購入して使用している。MT9T031は48MHzで動作している。2048x1536ピクセルのCMOSカメラだ。

DVI表示用ICは、XUPV5-LX110Tに搭載されているCH7301Cを使用している。出力画面は、1024x768のXGAでRGB各8ビットずつになっている。

画像はMIGを使用して、DDR2-SDRAMのSO-DIMMモジュールにバッファしている。

(注:ディスプレイ画面は一部、ガウスフィルタでぼかしてあります)

綺麗に映っていると思う。

なお、カメラからのクロックはDCMに入力してはおかしくなるようだ。現在は、BUFGを通して直接内部クロックの1つとして使用している。