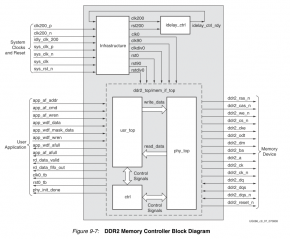

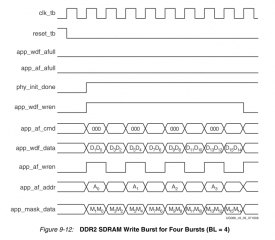

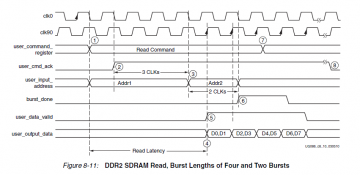

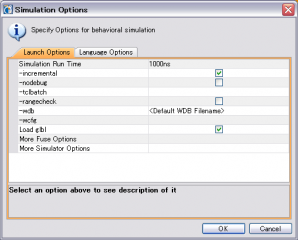

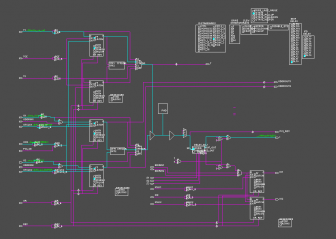

自作DDR2 SDRAMコントローラのユーザー・インターフェースは、Virtex-5のMIGのように、FIFOを使用していて、ほとんど同じプロトコルになっている。Spartan-3AのMIGも同様のプロトコルだったら、CMOSカメラ・ディスプレイ回路で自作IPと置き換えて確かめてみようと思ったが、IOパッドを固定するところで、エラーが出てしまった。更に、プロトコルも違ってるので、ラッパー回路を作る必要があるので、諦めることにした。

現在動作している自作DDR2 SDRAMのIPがあるので良しとした。一応、MIGの使い方はひと通りやってみることができた。Virtex-5のMIGは使おうと思っている。

これで、MIGの勉強はとりあえず終了とする。